## **HRM Quickstart Guide**

The SensL HRM-TDC is a 4-channel time-to-digital converter. It is effectively a very accurate stop-watch that measures the time interval between two signals. Since it has 4 channels, it can carry out this measurement independently and simultaneously for 4 different detectors or experiments. The instrument is controlled via USB from the PC, and this connection also allows data to be stored, and results displayed, on the PC.

This document is intended as an aid to the new user who may not have previous experience with using timing modules, or for anyone who would like a practical introduction to the HRM system. This document works through the initial setting up of the instrument and then goes on to provide a simple demonstration of the HRM-TDC working. The demonstration described here uses minimal additional equipment, just some cables and a connector.

#### SETTING UP THE HRM-TDC

For full technical details on setting up the HRM-TDC module, the user should refer to the User Manual. This Quickstart document will repeatedly make reference to specific pages in the User Manual so it is worth having a local copy on your PC.

The HRM-TDC module should be used on a secure surface, within comfortable reach of a mains power supply outlet and the PC that will be used for acquisition (the USB cable is 2m long, the power cable 3.3m long). Once set up, the HRM-TDC will have five or more cables connected to it, so ensure that sufficient space is available to accommodate these without creating a confusing tangle. The HRM-TDC has M6-threaded mounting holes on the underside allowing it to be securely mounted.

Once the module and accessories are unpacked (page 6 of the User Manual), the software installation procedure should be performed (page 18 of the User Manual). Take care to follow this procedure carefully, as any missed steps could result in the module not communicating with the PC properly. **Do NOT connect the HRM-TDC module to the PC until the installation procedure requires it.**

Once the installation is complete, the demonstration on the following pages can be carried out.

#### MEASURING THE JITTER OF THE HRM-TDC INTERNAL CLOCK

This demo uses a T-connector to take the HRM-TDC's own clock signal and use this as the input for both the START and STOP signals. The system then gives a measurement of the jitter of the internal clock.

## What you will need

- HRM-TDC module connected to power and PC

- PC running the SIE

- SMA T-connector and two SMA-SMA cables.

## Set-up

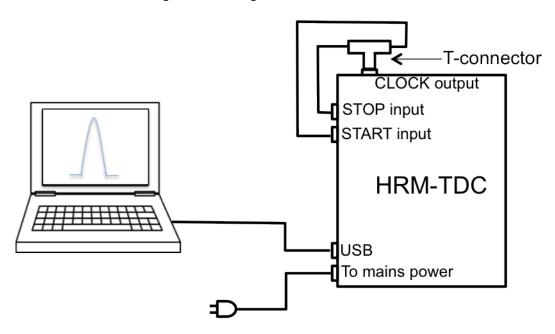

Attach the T-connector to the clock output SMA on the HRM-TDC module, as in Figure 1. Use the cables to connect the two ends of the cables to the START and STOP inputs of a single channel, i.e. make sure that both inputs are from the same channel, i.e. channel 0, OR channel 1 etc. Note that SMA connectors are threaded and so need to be screwed in hand-tight to ensure good connection.

Figure 1, Set-up for Demo

Once these connections are made, open up the SIE on the PC. Ensure that the HRM-TDC module is powered and connected via USB to the PC. You should see the module appear on the main screen of the SIE in the tab called 'Devices' on the left hand side. This is shown on page 19 of the User Manual. Select 'TCSPC' mode on the SIE. This mode can be thought of as a single-stop, histogram mode. You can read more on page 14 of the User Manual. The SIE settings for this mode are described on pages 20 - 22.

The default settings that are loaded up into the SIE should allow the demo to work, but it is important that the correct channel is enabled. For reference, the settings are listed in the following table;

| Variable              | Setting                                  |

|-----------------------|------------------------------------------|

| Clock Enable          | Check (tick) this box                    |

| Clock Hi              | 500ns                                    |

| Clock Lo              | 500ns                                    |

| External clock period | (leave blank)                            |

| Reverse plot          | Unchecked                                |

| Show the bins as bars | Unchecked                                |

| Microtime LSB         | 0 (27ps)                                 |

| Channel Enabled       | Check the box of the channel being used. |

| Start on rising edge  | Check the box of the channel being used. |

| Start on falling edge | Unchecked                                |

| Stop on rising edge   | Unchecked                                |

| Stop on falling edge  | Check the box of the channel being used. |

When these values are entered or edited, click "Apply". Once the configuration values are entered and applied, the configuration page can be removed by clicking on the X tab to display the graph section only. To start processing, click on the green right arrow at the top of the page. This can be repeated numerous times to display multiple traces on the same graph.

## Results

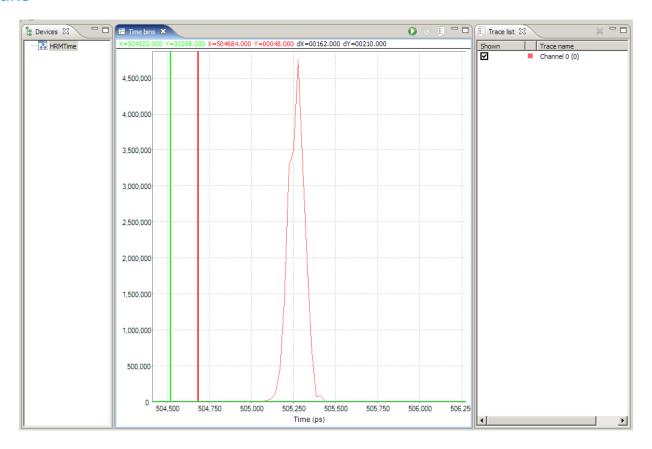

Figure 2, Typical jitter plot in TCSPC mode. The FWHM of this peak is the jitter.

# HRM Quickstart Guide

TECHNICAL NOTE

After a short amount of time, a peak like that in Figure 2 should appear. The FWHM of this peak represents the jitter on the signals, and in this case, of the HRM-TDC internal clock. The .CSV file containing the histogram data can be used to plot and fit the peak to extract the FWHM on appropriate software.

#### **GLOSSARY**

- **TDC** Time to Digital Converter, an instrument that accurately measures time intervals between two signals.

- **CFD** Constant Fraction Discriminator, an instrument that provides a constant trigger point for pulses of varying amplitude and necessary for high resolution timing.

- **SIE** SensL Integrated Environment, the GUI that runs on the SensL DLL and provides an example program allowing the user to make measurements with the HRM-TDC.

- **Timing resolution** Smallest interval of time accurately measurable, and is equal to the FWHM jitter of the system.

- **LSB** Least Significant Bit: The right most bit in a binary integer, and in the case of the HRM-TDC it determines the minimum timing resolution possible.

- TTL Transistor-Transistor Logic, High 2.2V 5V, Low 0V 0.8V.

- **SMA** SubMiniatureA, a coaxial RF connector with  $50\Omega$  impedance. The connector is threaded and so should be screwed in hand-tight to ensure a good connection.